# RayCore: A ray-tracing hardware architecture for mobile devices

Jae-Ho Nah<sup>1,3,4,5</sup>, Hyuck-Joo Kwon<sup>1</sup>, Dong-Seok Kim<sup>1</sup>, Cheol-Ho Jeong<sup>2</sup>, Jinhong Park<sup>3</sup>, Tack-Don Han<sup>4</sup>, Dinesh Manocha<sup>5</sup>, and Woo-Chan Park<sup>1</sup>

<sup>1</sup>Sejong University, <sup>2</sup>Siliconarts, <sup>3</sup>LG Electronics, <sup>4</sup>Yonsei University, <sup>5</sup>University of North Carolina at Chapel Hill

- Ray tracing (RT) [Whitted 1980]

- Classic rendering algorithm for photo-realistic rendering

Our goal

"Real-time" ray tracing dynamic scenes on

"mobile devices" for triangulated models

- Why mobile ray tracing?

- High interest in generating photo-realistic images at low power cost

- <u>Ray tracing H/W</u> can be a solution for mobile graphics

### Demo

RPU/D-RPU

TRaX

[Woop et al. 2005/2006] [Spjut et al. 2009]

## T&I Engine [Nah et al. 2011]

Mainly focus on high-quality rendering on <u>desktop PCs</u>

• A large chip area & high power consumption for high performance

### **Related Work: Mobile RT**

- Mobile environment

- Very limited area and power budget (~20 mm<sup>2</sup>, ~2 W for a GPU)

SMP2

OB

S/W approach MobiRT

[Nah et al. 2010]

H/W approaches MRTP SGRT 0 [Kim et al. 2012, 2013] [Lee et al. 2012, 2013] OB OB T&I Unit Multi-core ARM SMP0 SMP1 VLIW Engine I-Cache ntersection Traversal C-Mem Coarse Graine Colo Unit Unit Reconfigurabl RAB0 DataS merger Array Cache(L1) Cache(L1) Crossba IMEM RABI Cache(L2) Internal SRAM CMEM CTRL RayGenerato Host System BUS AXI System BU

Host DRAM

Either no real-time performance or results based on S/W simulations

Texture

Unit

Cache(L

External DRAM

### **Main Results**

previous mobile RT H/W

Similar to current mobile GPUs

# Overall H/W Architecture & Design Decisions

Mobile Media Processor Lab. Sejong Univ.

### **Design Decisions**

Mobile Media Processor Lab. Sejong Univ.

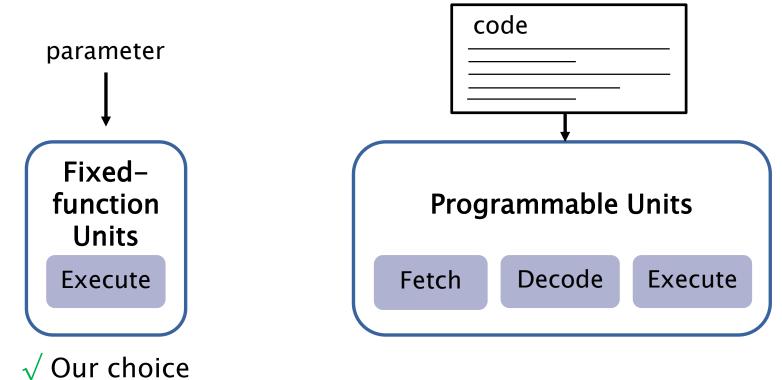

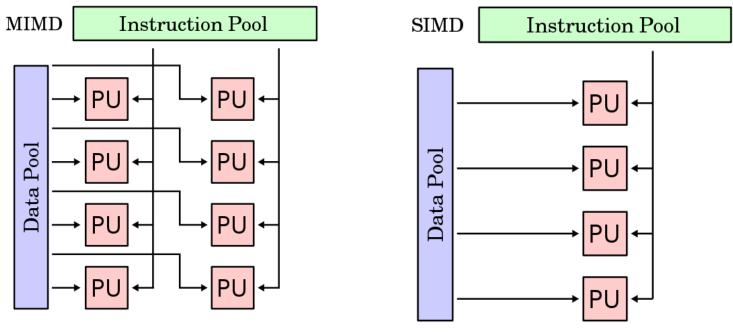

Fixed-function units vs programmable units

• High area and power efficiency

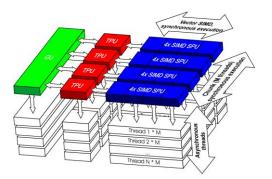

#### MIMD vs SIMD

$\sqrt{Our choice}$

• High H/W utilization regardless of ray coherence

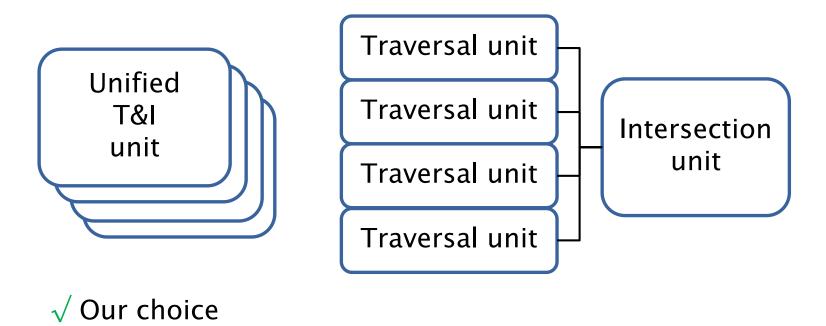

Unified traversal & intersection (T&I) units vs separate T&I units

• No load imbalance problem in prior separate T&I units

### **Design Decisions**

#### $\sqrt{Our choice}$

Reuse existing buffers/registers to minimize additional register files

### **Design Decisions**

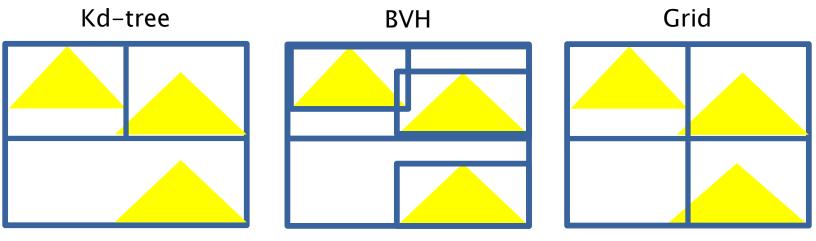

Acceleration structure (AS)

$\sqrt{0}$  Our choice

- Fast traversal with early termination

- Good cache efficiency with a small node size (8 bytes)

- Our H/W tree builder solves the tree-build time problem

### **Rendering effects**

Full Whitted ray-tracing effects

**Specular reflection**

Refraction

Shadows

### **Rendering effects**

Distribution ray-tracing effects

#### Ambient occlusion (AO)

#### **Diffuse inter-reflection**

### **Rendering effects**

Inverse displacement mapping

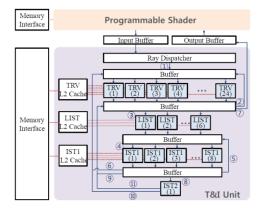

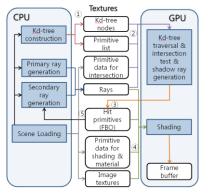

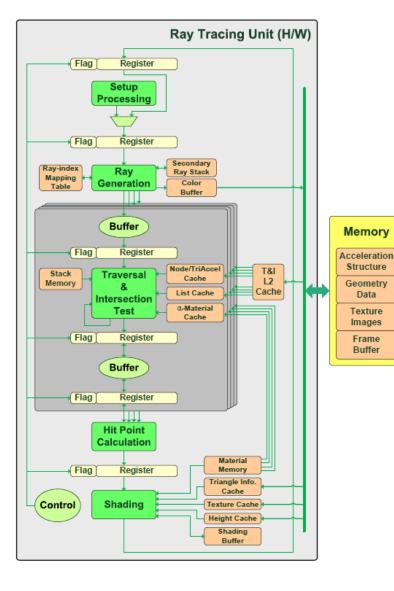

### Ray-Tracing Unit (RTU) & Tree-Building Unit (TBU)

- Setup-processing unit

- Ray-generation unit

Multiple traversal & intersection (T&I) units

- Hit-point calculation unit

- Shading unit

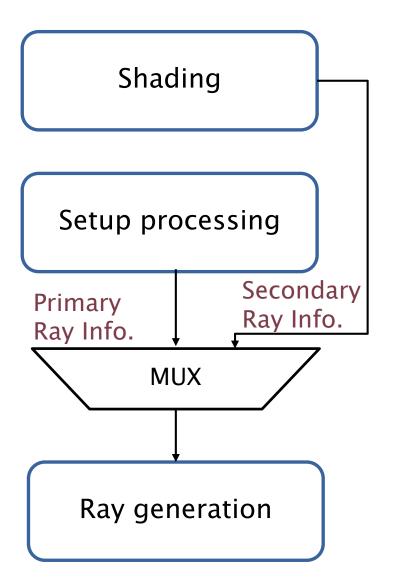

### **Setup Processing & Ray Generation**

- Initialize primary-ray information (ray type+ray index)

- Pass secondary-ray information defined by the shading unit

Generate primary/ secondary/shadow rays

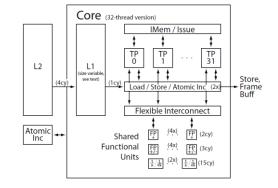

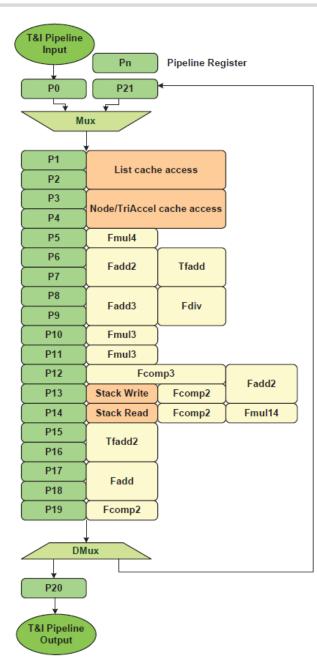

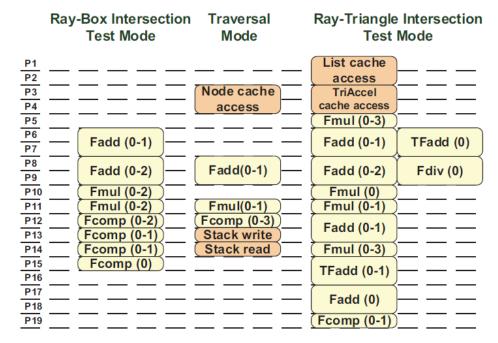

### **Unified T&I Pipeline**

#### A single pipeline with three modes

- No load imbalance problem

- Greatly simplified control logic and interfaces between units

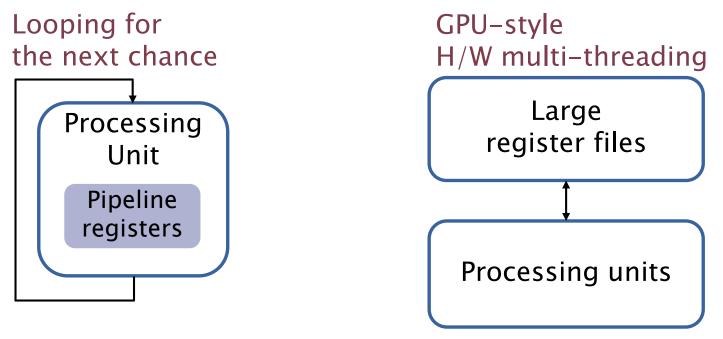

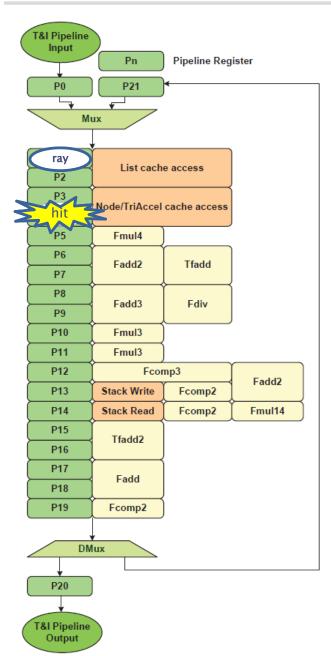

### **Looping for the Next Chance**

Simple multi-threading technique

#### Operation

- Cache miss  $\rightarrow$  idle

- Next loop  $\rightarrow$  reactive

- A cache miss acts as prefetching data

#### Pros

- Ease of H/W implementation

- Use of existing internal memory (input/output buffers & pipeline registers)

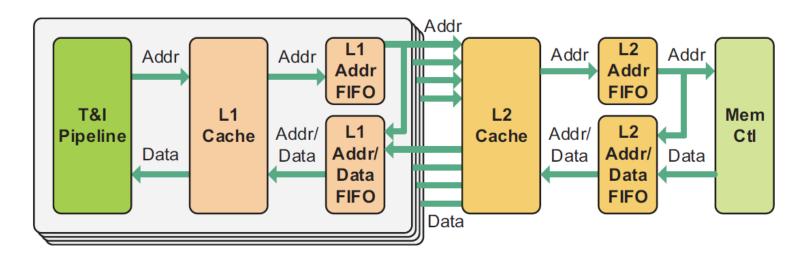

### Memory System of the T&I unit

- Two-levels of caches (L1/L2)

- L1/L2 Address FIFO for handling memory requests

- L1/L2 Address/Data FIFO for delivering address & data to the upper-level cache

### **Hit-Point Calculation and Shading**

- Hit-point calculation

- Calculate the final (x,y,z) position

$p(t) = o + t \cdot d$

- Shading

- Phong illumination

- Texture mapping with bilinear filtering & mip-mapping

- Inverse displacement mapping

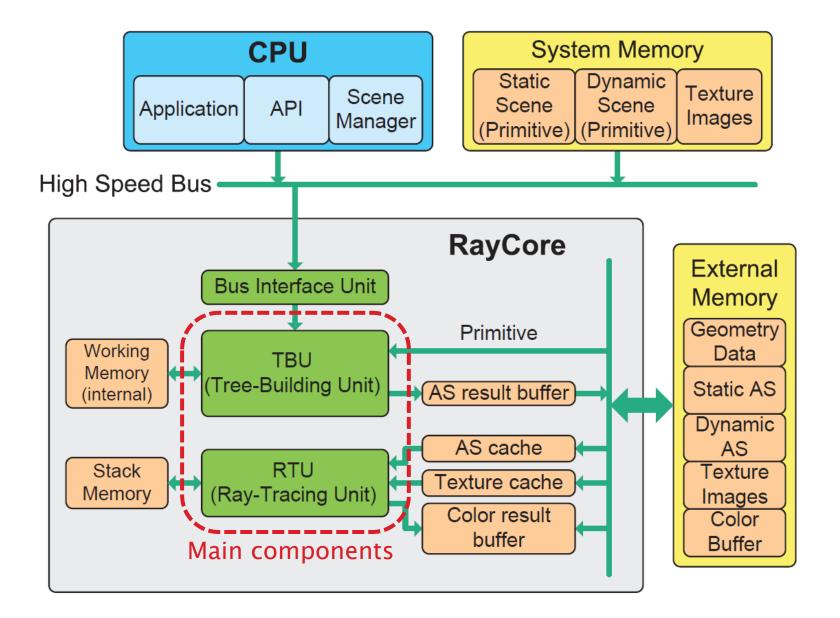

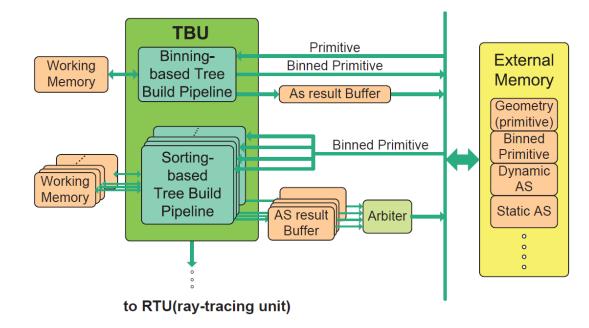

### **Tree-Building Unit (TBU)**

- Two pipeline types

- Binning for upper-level nodes + sorting for lower-level nodes

- Fast kd-tree construction without significant tree-quality degradation

- Memory traffic reduction techniques

- Internal working memory for local tree-building procedure

- Node scheduling for burst memory accesses

### **Ray Tracing API**

#### OpenGL ES 1.1-like API

- Provides similar interfaces to OpenGL ES programming

- Static objects/tree are retained for subsequent frames

- Dynamic objects/subtrees are updated during each frame

- Complete specification and its programming guide are provided on the Siliconarts homepage (<u>www.siliconarts.com</u>)

```

// set a box

rcStaticSceneBegin();

...

...

rcVertexPointer(3, RC_FLOAT, 0, box);

rcGenMaterials(1, &material_box);

rcBindMaterial(material_box);

rcMaterialf (RC_FRONT_AND_BACK, RC_REFLECTION, 0.0f);

rcMaterialfv(RC_FRONT_AND_BACK, RC_DIFFUSE, &cyan.r);

rcDrawArrays(RC_TRIANGLES, 0, 30);

rcDisableClientState(RC_VERTEX_ARRAY);

```

rcStaticSceneEnd();

### Implementation and Results

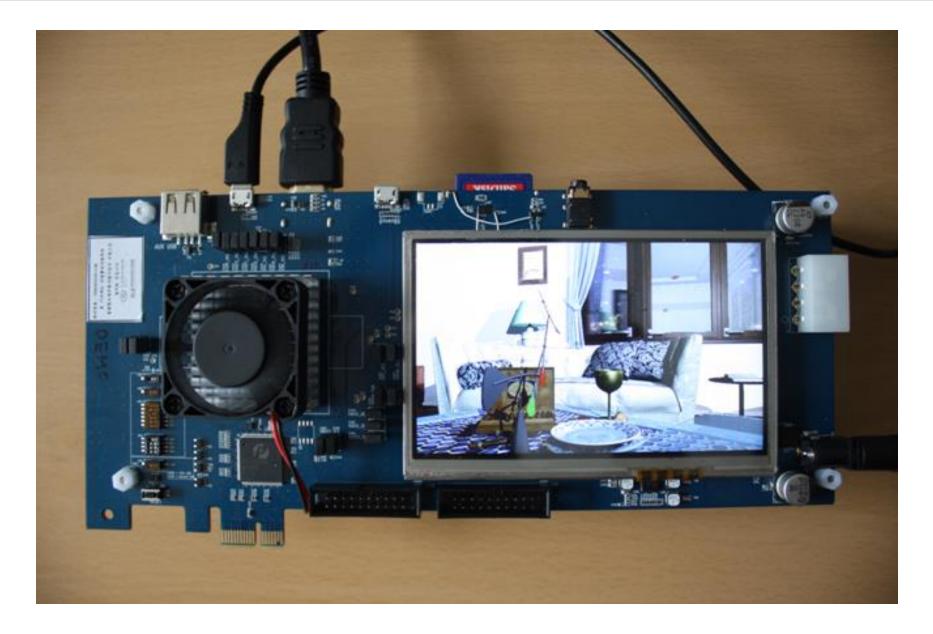

### **FPGA** Prototype

#### iNEXT-V6 board

- 2 Xilinx Virtex-6 LX550 FPGA chips

- 2 GB of DDR3 RAM & 8 MB of SRAM

- A TFT LCD board with 800x480 resolution

- PCI Express interface

- Our implementation

- 4 FPGA chips for 4 RTUs (with 2 iNEXT-V6 boards)

- 1 FPGA chip for 1 TBU

- 84 MHz core and memory clock

- Total required SRAM: 507KB for an RTU and 218KB for a TBU

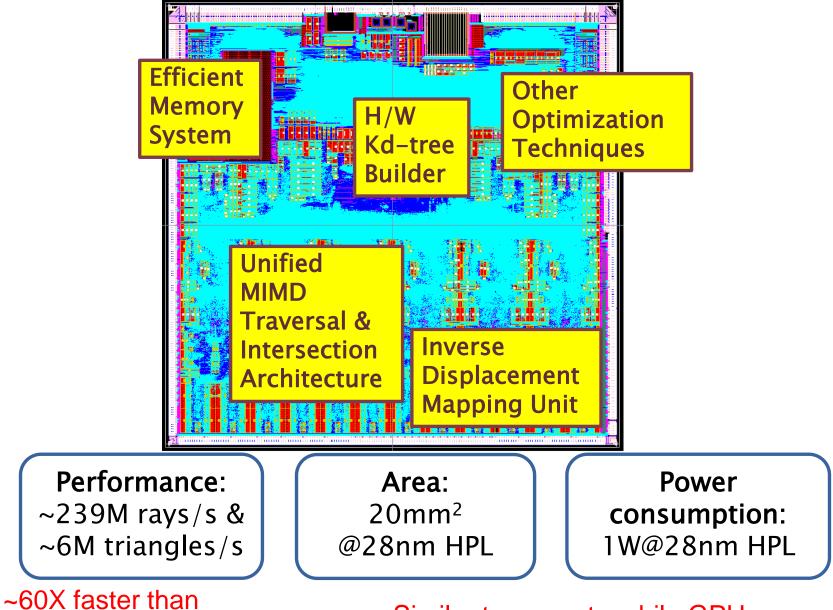

### **ASIC Evaluation**

- TSMC's 28 nm HPL process and Synopsys design compiler

- Clock frequency: 500MHz@0.9V

- Area: 3mm<sup>2</sup> per RTU (18mm<sup>2</sup> for 6 RTUs) + 1.6mm<sup>2</sup> per TBU

- Internal power consumption : 1W for 6 RTUs and 1 TBU

- Particularly suitable for mobile devices

### **RT Performance on the FPGA**

#### Whitted ray tracing

Moving light

Living room

- 4 RTUs @ 84MHz

- 3-5 rays per pixel

- Performance: 23-26 Mrays/s

- Memory traffic: 46-122 MB/s

- FPS: 13-21 @ 840 X 480 resolution

- Interactive frame rates

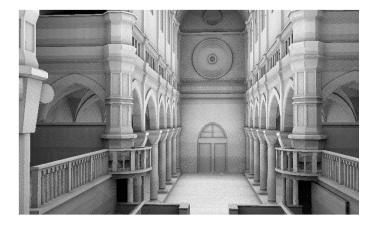

### **RT Performance on the FPGA**

Distribution ray tracing

Conference

Sibenik

- 4 RTUs @ 84MHz

- 2 (primary), 16 (AO), 32 (diffuse) rays per pixel

- Performance: 21 (primary), 23 (AO), 18–20 (diffuse) Mrays/s

- Memory traffic: 8-62 (primary / AO), 420-605 (diffuse) MB/s

- Low performance degradation when tracing incoherent rays

### **RT Performance on the FPGA**

## Inverse displacement mapping (IDM) <u>BART</u> Kitchen

(IDM off)

(IDM on)

- 4 RTUs @ 84MHz

- Performance: 18-20 Mrays/s

- 30% increase of memory traffic to access the height map

- Detailed results are included in

Kwon *et al.*, Effective traversal algorithms and hardware architecture for pyramidal inverse displacement mapping, *Computers & Graphics*, 2014

### **KD-tree Construction Performance**

- Performance (1 TBU)

- 1.6~117.9 ms/frame @ 84MHz for 0.6~64K triangles

- 0.4~1M triangles/s

- Memory traffic

- 0.1~36.1 MB/frame

Performance Evaluation of the ASIC Ver.

#### Mobile Media Processor La Sejong Univ.

#### RTU performance

- 9X faster than the FPGA ver. ( $84 \rightarrow 500$  MHz &  $4 \rightarrow 6$  RTUs)

- ~239M rays/s & 56 FPS@720p

- TBU performance

- 6X faster than the FPGA ver. ( $84 \rightarrow 500$  MHz & 1 TBU)

- 2~6M triangles/s

- Required memory bandwidth

- 1.1GB/s on 6 RTUs for Whitted ray tracing

- 1.1GB/s on 1 TBU for 30FPS kd-tree construction

- Much less than the bandwidth of dual LPDDR3 1333MHz (12.8GB/s)

### **Preliminary Comparison**

Ray-tracing performance in the Conference scene

GPU MIC Mobile RayCore [Gribble and [Benthin et RT H/W ASIC Naveros 2013] al. 2012] [Kim et al. (ours) 2013] Mrays/s 500 210 4 239 Intel MIC Platform Reconf. **RTU NVIDIA GTX690** SIMT Process(nm) 28 45 90 28 915 50-400 500 Clock (MHz) 1200 18 (6 RTUs) Area (mm<sup>2</sup>) 16 294 X 2 300 (TDP) 0.2 Power @100MHz (RTU+TBU) consumption(W)

- Desktop-level performance

- Mobile-level area and power consumption

#### KD-tree construction performance

|                                 | CPU<br>[Shevtsov et al. 2007] | GPU<br>[Hou et al. 2011] | RayCore ASIC<br>(ours)       |

|---------------------------------|-------------------------------|--------------------------|------------------------------|

| Time to build<br>a kd-tree (ms) | 27                            | 38                       | 20                           |

| Scene<br>(# of tris)            | Bunny<br>(69K)                | Robots<br>(71K)          | Transparent<br>Shadows (64K) |

| Platform                        | Intel Core2 Duo X 2           | NVIDIA GTX280            | TBU                          |

| Process                         | 65                            | 55                       | 28                           |

| Clock (MHz)                     | 3000                          | 1476                     | 500                          |

| Area (mm²)                      | 143X2                         | 576                      | 1.6 (1 TBU)                  |

| Power<br>consumption(W)         | 65 X 2 (TDP)                  | 236 (TDP)                | 1 (RTU+TBU)                  |

Comparable performance to CPU/GPU approaches

& much less H/W resources/power consumption

### Conclusions, Limitations, and Future Work

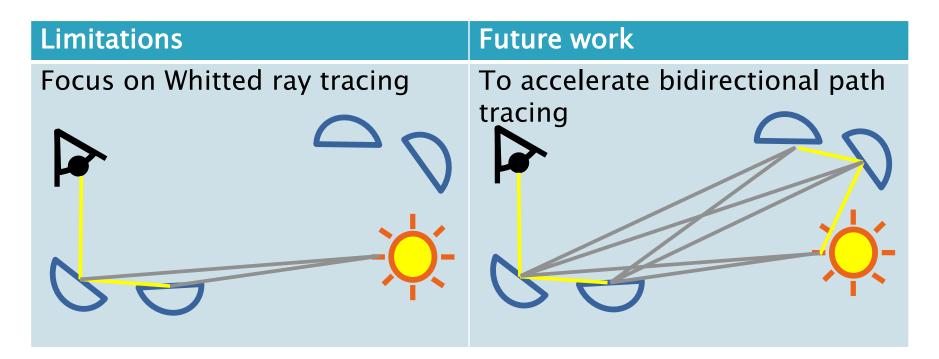

| Limitations                  | Future work                              |  |

|------------------------------|------------------------------------------|--|

| Focus on Whitted ray tracing | To accelerate bidirectional path tracing |  |

| Fixed pipelines              | To combine with programmable shaders     |  |

| RTU                          | RTU GPU                                  |  |

| Limitations                                   | Future work                                                |

|-----------------------------------------------|------------------------------------------------------------|

| Focus on Whitted ray tracing                  | To accelerate bidirectional path tracing                   |

| Fixed pipelines                               | To combine with programmable shaders                       |

| High memory traffic on incoherent ray tracing | Additional ray-sorting logic<br>Ray<br>sorting<br>RTU DRAM |

| Limitations                                   | Future work                              |

|-----------------------------------------------|------------------------------------------|

| Focus on Whitted ray tracing                  | To accelerate bidirectional path tracing |

| Fixed pipelines                               | To combine with programmable shaders     |

| High memory traffic on incoherent ray tracing | Additional ray-sorting logic             |

| Only support kd-trees                         | To support both kd-trees and BVHs        |

|                                               |                                          |

| Kd-tree                                       | Kd-tree BVH                              |

|                                               |                                          |

### Conclusions

- A new hardware ray tracer for mobile devices including

- Unified T&I pipelines

- H/W kd-tree builder

- Other various novel techniques

- RayCore can be used for various mobile applications

- Games, UX, AR, etc.

- High-quality images & simpler programming

Mobile Media

Seiona Univ

### Acknowledgements

#### Siliconarts, NRF, ARO & NSF